SOI-始終無法兌現天賦的半導體技術?

日期:2021/03/21

文:B.H.Huang / 校稿: Y.C.Lo

閱讀程度:簡單

閱讀時間:8 min

在半導體發展的歷史上,為了讓晶片運算能力更強,電晶體不斷地朝著更小尺寸、更加省電的方向發展,例如三五族半導體就是運用特殊的材料特性來減少電子設備所需體積;FinFET 則在電晶體結構上做出創新、成功打下未來幾十年的半導體基礎。

話說當年呀,胡正明推出 FinFET 這個新一代電晶體的時候,其實他還提出了另一種新型的半導體- SOI,然而,不同於 FinFET 的倒吃甘蔗、大紅大紫,這位 SOI 的命運卻是大不相同啊……

SOI 你誰?

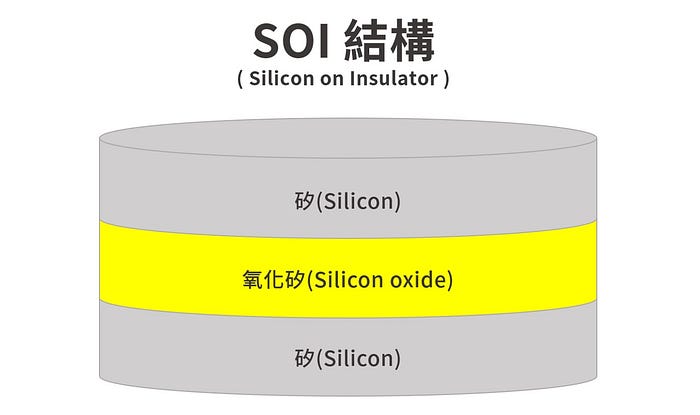

SOI,全名為 Silicon on Insulator,Insulator 意思是絕緣體,也就是不導電的物質。就如同字面上的意思,SOI 的結構總共有三層,從上到下分別為矽、氧化矽、矽,中間的氧化矽即是充當絕緣體的角色,如同三明治的結構。

因此,這種構造,相對於整顆電晶體都是矽的 MOSFET 來說,SOI 做成的電晶體在原本的 Channel 下方多出一層絕緣體。這樣的好處在於那層薄薄的絕緣體可以擋住電晶體裡到處流來流去的「漏電流」,這樣不只電晶體可以更好地控制電流,還更加省電。

在《FinFET-摩爾定律的救世主》這篇我們提過當電晶體不斷地縮小尺寸時,因為漏電的關係導致耗電功率不斷變大,而上述的 SOI 很好地解決了這個困難,在縮小尺寸的同時還保證了電晶體的性能。這樣看來,似乎 SOI 就是未來半導體材料的不二人選了?

理想很豐滿,現實很骨感

儘管 SOI 擁有比一般電晶體漏電更低的優勢,然而實際製作卻會遇到一個問題:當把氧化矽再往上疊另一層矽時,會很難直接疊上去。這是因為氧化矽的原子排列很混亂,無法和上面的矽原子很好地結合,就如同一座房子如果地基不夠堅固牢靠的話,上面的建築物再怎麼整齊也一樣蓋不起來,因此, SOI 的問題可說是「下樑不正上樑歪」。

為了克服這個先天劣勢,聰明的科學家和工程師想出了幾種方法來製作出SOI的結構。

方法一:氧離子植入法

此方法直接將高能量的氧離子打入矽晶圓中,再透過一系列的加溫步驟,讓這些氧離子與裡面的矽原子結合,把中間的矽變成氧化矽,即得到 SOI 的結構。

不過打完氧離子的矽晶圓,就像挨了子彈的盾牌一樣,內部的原子已經被打亂了,即使後續的製程會修復,但仍對晶圓造成不小的傷害呢!

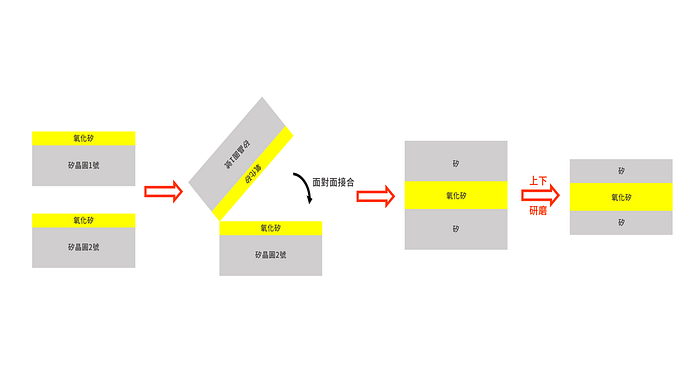

方法二:接合法

一般的矽放在空氣中其實表面就會慢慢氧化,而我們可以利用加熱的方式加速氧化過程,接著將氧化過的矽晶圓直接面對面接合起來,再把上下多餘的矽磨掉就完成了。

這個方法簡單直接,缺點卻也顯而易見:接合需要用上兩倍量的材料,才能做到跟別人面積大小一樣的 SOI 晶圓,生產成本相當的高。

因此,不論是上述何種方法,SOI 都在製造技術或是生產成本上都存在許多問題,這也是為何過去幾十年來 SOI 較少被採用的原因。

柳暗花明又一村?

由 SOI 這個案例,我們可以發現即使一個技術理論再怎麼完美,實際落地執行時仍會因為製作技術的限制、商業模式上的考量而不被產業界內的公司採納。

反過來說,儘管「傳統矽晶圓」在各種半導體特性中也不是表現最好的,然而,正因為矽的易取得性、製程穩定、與其他元素相容性高的特質,讓它一直以來都是半導體產業最常被採用的晶圓製造技術。(推薦影片:Why is Silicon Used for Computer Chips?)

有趣的是,由於這幾年 5G 科技的興起,因為操作頻率高的關係,對於電晶體的要求每秒要開關非常多次,這時 SOI 漏電少、耗電功率低的特性顯得更加重要,再加上它的製作成本、製程難度等都約介於「傳統矽晶圓」以及「三五族半導體材料」間,於是 SOI 成為了許多科技廠另一個積極發展的方向。(延伸閱讀:成本/性能皆具水準,FD-SOI 勢力崛起- 電子工程專輯)

究竟沉寂了好幾年的 SOI,是否有機會在 5G 時代大放異彩呢,成為暨矽和三五族半導體的另一個解答呢?就讓我們靜靜期待吧~

謝謝看完這篇文的你~

看完這篇文,可以幫我們按 5下clap!

看完而且喜歡的話,可以幫我們按 15下clap!

如果想看我們繼續寫更多文章的話,直接拍到 25下吧!

最後想了解更多 SemiKnow 的話,歡迎追蹤按讚我們的粉絲專頁: